颖崴7月营收6.26亿元月增66.34% 创历年同期新高

...个,预计参展人潮超过10万人次,矽光子、异质整合、小晶片(Chiplet)、3D IC、面板级扇出型...

...个,预计参展人潮超过10万人次,矽光子、异质整合、小晶片(Chiplet)、3D IC、面板级扇出型...

...合作伙伴,以及许多人在说摩尔定律放缓,AMD专注于小晶片(Chiplet)领域发展,这是AMD很重要...

...算架构提供高密度可扩展封装平台。」 此技术可实现小晶片(Chiplet)与高频宽记忆体(HBM)的...

...I 应用在再生能源、智慧医疗与全球半导体人才培育的最新实例,揭示一颗小小晶片如何驱动改变世界的力量。

英特尔同步宣布多项生态系扩展计划,包含「晶圆代工小晶片联盟(Chiplet Alliance)」与「...

...湾在全球智慧显示领域持续发光发热。 为满足AI与小晶片所需的先进封装需求,产业技术司补助工研院研发...

...技术在制程、封装和测试等方面仍面临挑战,例如如何缩小晶片尺寸并降低成本、光子电路的能量损耗、光子晶片...

...5的堆叠层数将达20层,并与更多逻辑装置整合於单一小晶片(Chiplet)架构中,台积电在CoWoS...

...解决方案,在未来高阶运算半导体封装,实现无处不在的小晶片异质整合互连,为业界提供整合的解决方案。 ...

...出,异质整合的先进封装是未来半导体发展的关键,透过小晶片(Chiplet)设计,以及晶片间的立体堆叠...

...问题是,AI晶片需要先进封装,来整合多个组件,称为小晶片(Chiplet)。 尽管台积电计划...

...方位(GAA)电晶体技术,能精确控制电流,进一步缩小晶片组件尺寸并减少漏电,对于高密度晶片设计尤为关...

...效能运算(HPC)及人工智慧(AI)领域,特别是在小晶片(Chiplet)封装、面板与晶圆级封装等新...

...片对晶圆键合更加灵活且具成本效益。通过SLT,超薄小晶片能在不同晶圆之间实现更小尺寸和更高的功能密度...

...AI 资料中心工作负载,并透过 Zen 5 核心与小晶片架构,为现代资料中心带来创新与卓越的运算效能...

...速度与5.2 GHz最高提升时脉注6,代表著X3D小晶片史上最高的时脉速度。120瓦的TDP功耗加上...

...当今不断演进的环境中,随著动态AI工作负载、客制化小晶片以及3D封装和系统架构的进步,建立一个强大且...

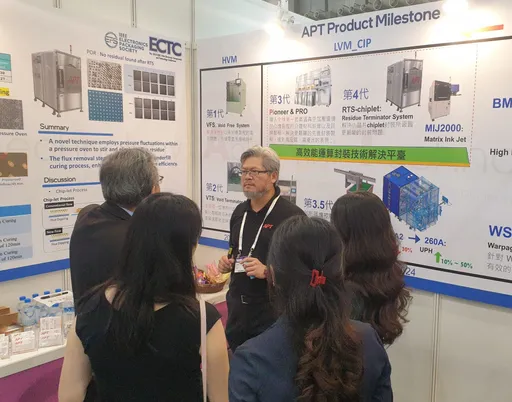

...行优化;彻底消除封装过程中的气泡和残留物,显著提升小晶片封装的良率和稳定性。 印能推出的BMAC(...

...外,随著AI、HPC、5G应用需求增加,先进封装和小晶片(Chiplet)等异质整合技术成为推动半导...

...来降低制程复杂度并改善晶片的生产周期。台积电并透过小晶片(Chiplet)先进封装技术,一举将8颗H...