印能8月营收2.59亿创单月营收新高 获工程界诺贝尔奖肯定

印能董事长洪志宏指出,在Chiplet先进封装中,高温熔焊扮演关键角色。随著晶片微缩与堆叠密度提升,...

印能董事长洪志宏指出,在Chiplet先进封装中,高温熔焊扮演关键角色。随著晶片微缩与堆叠密度提升,...

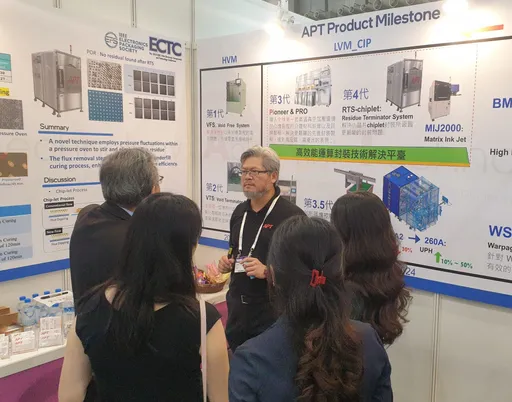

...。大会9月8日以系列论坛揭幕,焦点锁定3D IC、Chiplet、FOPLP、矽光子、HBM记忆体、...

...决方案」提供完整的AI、HPC方案,满足先进封装、Chiplet、系统级封装(SLT)等市场需求。 ...

...场占有率与技术实力兼备,正持续受惠于AI、HPC、Chiplet异质整合等产业趋势所带来的强劲需求。...

...参展人潮超过10万人次,矽光子、异质整合、小晶片(Chiplet)、3D IC、面板级扇出型封装(F...

...技术创新突破,后段封装也展现多元进展,如HBM整合与Chiplet晶粒设计,为营收增长创造更多机会。

...WoS-S 正逐步转向更高整合度的CoWoS-L Chiplet Die 架构,InFO-POP也发...

...因2奈米制程导入极紫外光(EUV)技术,以及AI与Chiplet架构设计的复杂度提升,营运表现维持稳...

...聚焦于前瞻技术革新与供应链重塑。内容涵盖3DIC、Chiplet、FOPLP、矽光子、HBM记忆体、...

...供高密度可扩展封装平台。」 此技术可实现小晶片(Chiplet)与高频宽记忆体(HBM)的紧密整合...

...宣布多项生态系扩展计划,包含「晶圆代工小晶片联盟(Chiplet Alliance)」与「价值链联盟...

...,以及许多人在说摩尔定律放缓,AMD专注于小晶片(Chiplet)领域发展,这是AMD很重要的发展方...

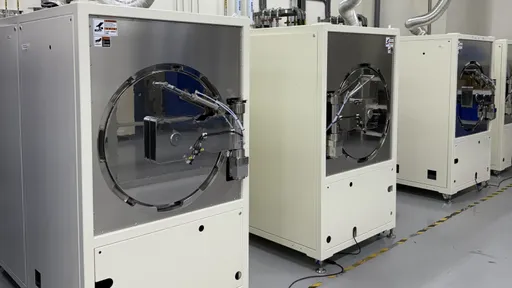

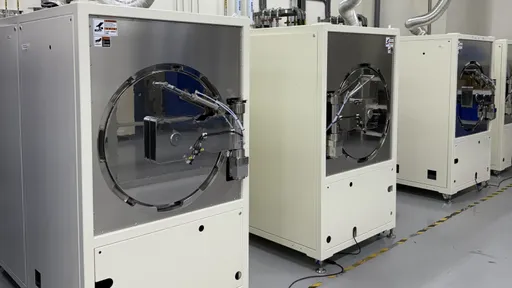

董事长洪志宏表示,印能在AI-Chiplet先进封装技术中扮演关键角色,特别是提供高压真空热流控制、...

...层数将达20层,并与更多逻辑装置整合於单一小晶片(Chiplet)架构中,台积电在CoWoS技术中的...

....6%,主因公司专注高阶产品布局,ABF载板受惠于Chiplet及2.5D先进封装需求大增,产能利用...

...的转变。美系手机大厂预计于下一代的 M5晶片 采用Chiplet晶粒分割设计,并透过3D封装技术进行...

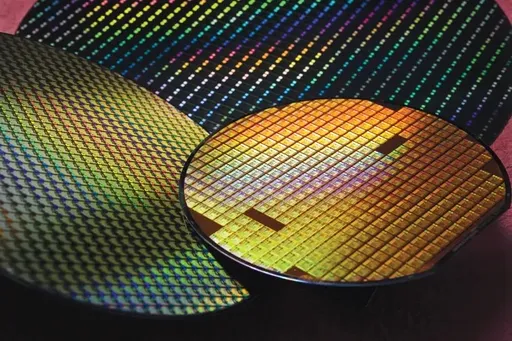

...整合的先进封装是未来半导体发展的关键,透过小晶片(Chiplet)设计,以及晶片间的立体堆叠技术,先...

...AI晶片需要先进封装,来整合多个组件,称为小晶片(Chiplet)。 尽管台积电计划在亚利桑...

随著半导体技术不断演进,Chiplet技术的兴起带来了新的挑战,除了气泡问题,还衍生出晶片背面爬胶问...

...展,由颖崴研发主管孙家彬分享在CPO、CoWoS及Chiplet等高阶封装趋势下,颖崴所提供的最新技...