专家观点:封闭 vs. 开放两大系统

矽光子 CPO 产业正逐渐分化为两大技术阵营。之光半导体技术长陈升祐博士指出,矽光子元件单价高、容错率低,若在封装后才发现缺陷,报废成本极高,因此测试环节大幅前移,「每颗必测」成为业界共识,推升探针卡、高阶电测设备需求,也带动材料与载板投资。

鸿海研究院半导体研究所洪瑜亨博士分析,AI 训练与推理带动频宽需求急遽攀升,如今资料中心超过七成时间耗在资料搬运等待;当单通道速率突破 200G 后,铜线在损耗、功耗与模组体积上全面受限,迫使光学功能必须贴近运算晶片。由此市场分化出 LPO(线性驱动可插拔光学) 与 CPO 两大路线,其中 CPO 将光引擎与 ASIC 直接整合至先进封装,缩短讯号路径、降低能耗,成为新世代 AI 资料中心的关键。

洪瑜亨补充,交换器大约每两年带宽就会倍增,但单通道速率需三至四年才翻倍,形成技术落差并推动 CPO 与 光学 I/O 加速发展。虽然 CPO 解决了传统 QSFP+ 模组在体积与讯号失真上的限制,但高度整合也带来 板翘曲与热管理 挑战,未来将朝更积体化的 光学 I/O 演进。

目前两大生态系如下:

封闭系统:以 NVIDIA 为代表,强调垂直整合与专属设计,并依靠台积电先进技术推进;与其合作的台厂包括上铨,掌握光纤阵列单元(FAU)与封装能力。

开放系统:由 Broadcom 主导,采标准化与模组化,利于广泛供应链参与,例如鸿海旗下讯芯-KY便与 Broadcom 合作,服务多家美系客户。

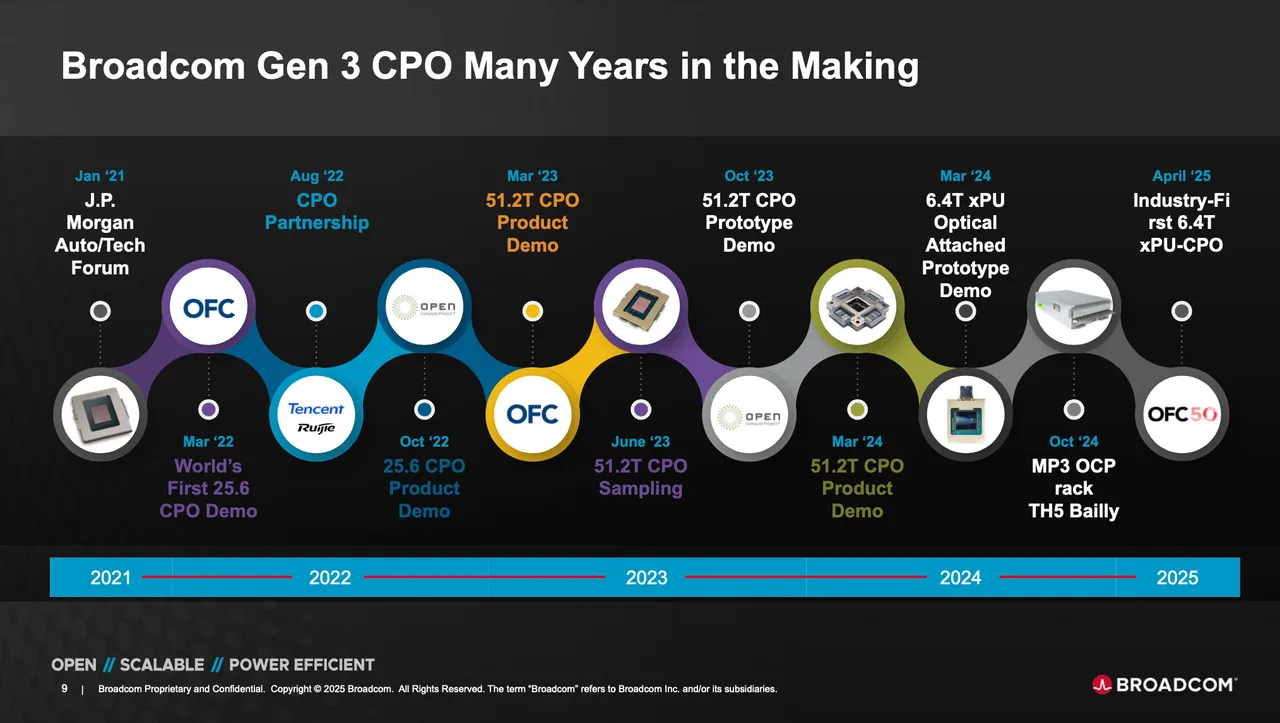

Broadcom领跑 CPO:开放生态加速商用

Broadcom 在光通讯与网路晶片耕耘已久,从 SerDes、高速交换晶片到光电整合技术,一直是超大规模资料中心的核心供应商。 Broadcom 光学系统副总裁 Manish Mehta 表示,AI 训练与推论对网路需求呈指数成长,传统铜缆难以支撑 Tbps 级资料吞吐,必须引入光学互连解决 I/O 与能效瓶颈。

Broadcom 自 2021 年布局 CPO,完成多代平台演进,2023 年起进入商用并推进 200G/Lane、400G/Lane 技术。CPO 将矽光子引擎与交换晶片同封装,功耗可降 3.5~4 倍、整合密度提升百倍,让过去需半机柜的光模组缩小到「手掌大小」。 Manish Mehta 预估 2027 年将是 CPO 商用临界点,届时可望逐步取代传统的可插拔式光收发模组(Pluggable Transceiver)成为主流。

Broadcom 同时积极推动 开放生态,选择标准化介面与模组化设计,吸引云端服务供应商、系统整合商与上游台厂参与,与 NVIDIA 专属的封闭系统形成鲜明对比。

相关新闻:矽光子突围01|光进铜退成趋势 台湾AI十大建设+产业联盟双引擎发动

相关新闻:矽光子突围02|加速落地!OBO到CPO三阶段演进 2027商用爆发、台厂迎转型契机

相关新闻:矽光子突围03|AI资料中心升级两大挑战 台湾供应链助攻成「梦想实现之地」

NVIDIA:封闭式 GPU 平台推进光电封装

相较 Broadcom 的开放策略,NVIDIA 正以自家 GPU 打造封闭式高速传输生态系。高级副总裁 Gilad Shainer 表示,AI 训练与推论需要同时连接数十万颗 GPU,任何延迟都可能让运算停滞并推高成本,因此长期投入 InfiniBand 与 Spectrum-X Ethernet,持续推进更高频宽与更低延迟的资料中心互连。

目前 NVIDIA 高频宽连接仍以铜缆为主,但随介面速度迈向 1.6T、3.2T,铜材受限于能耗与距离,转向光学互连势在必行。市场预期未来高阶 GPU 平台,也就是明年将推出的 Rubin平台,将采用混合式光电封装以突破光学 I/O (OIO)瓶颈。

在元件设计上,NVIDIA 偏好 MRM(微环调变器),利于 SoC 微缩与高整合,但需克服温度敏感与热补偿挑战,而NVIDIA则是依靠台积电一流的制造技术,让 MRM 从一个风险较高的选项,成为可以进行的战略赌注;Broadcom 则采MZI(马赫增德干涉器),并以此为基础打造的 MZM(马赫增德调变器),虽体积较大但稳定性高。除了Broadcom,包括Marvell、Intel也都采用MZM解决方案。专家认为两者无绝对优劣,矽光子仍处于多路线并行探索期。

台积电矽光子解方:COUPE结合CoWoS

台积电在 OCP APAC 与 矽光子国际论坛 上强调,为满足 AI 客户对高频宽、低功耗需求,2026 年将导入 CPO 量产。公司以 12 吋 SOI(绝缘层上覆矽)晶圆 为核心,结合异质整合与先进封装,让矽光子真正走向商用。

三大技术优势包括:

精准制程:波导线宽变异可控在 2 奈米内,确保微环共振腔等高灵敏元件一致性。

异质整合封装:透过紧凑型通用光子引擎(Compact Universal Photonic Engine,COUPE) 与 CoWoS,实现数百通道光 I/O,降低功耗与延迟。

晶圆级测试:支援 Wafer-Level 与 Chip-Level 测试,提早筛选良率晶粒,降低封装后重测与报废成本。

根据台积电 2024 年北美技术论坛,COUPE 采用 SoIC-X 晶片堆叠技术,将电子裸晶直接堆叠于光子裸晶上,相较传统堆叠方式,能达到更低电阻与更高能源效率。台积电与 Ansys、Synopsys、Cadence 等 EDA 厂商合作推进,2025 年将完成支援小型插拔式连接器的验证,2026 年整合 CoWoS 成为 CPO 元件,让光连结直接导入封装。

台积电指出,CPO 商业化仍面临三大挑战:制程良率控制、测试标准缺乏及封装热管理。但凭借高良率制程、成熟测试平台与异质整合封装能力,台积电已成 Broadcom、NVIDIA 等系统大厂不可或缺的核心伙伴,被视为推动矽光子量产的关键推手。

投资观察:2027商用关键点 台湾供应链迎新红利

CPO 与矽光子已从实验室走向商用化前夜,Broadcom 推动开放生态、NVIDIA 巩固封闭系统,两大路线加速分化;台积电凭借制程、封装与测试整合稳居全球核心供应商。法人普遍认为 2027~2028 年是商业化关键点,届时无论是测试与封装、材料与 SOI 晶圆,还是模组与光学元件,台湾厂商都将在全球 AI 高速互连浪潮中扮演不可或缺的角色,成为下一波 AI 投资布局的受益族群。

點擊閱讀下一則新聞

點擊閱讀下一則新聞