Lam Research 全球产品事业群资深副总裁 Sesha Varadarajan 指出,VECTOR TEOS 3D 能沉积业界最厚、且无空隙的晶片间介电层薄膜,并可根据先进堆叠方案的严苛需求进行客制化,即便在高应力、翘曲严重的晶圆环境下也能适用。他强调,该设备是 Lam 在先进封装解决方案组合中的新成员,能提供差异化的原子级创新,协助晶片制造商突破摩尔定律的限制,迎接 AI 驱动的新世代。

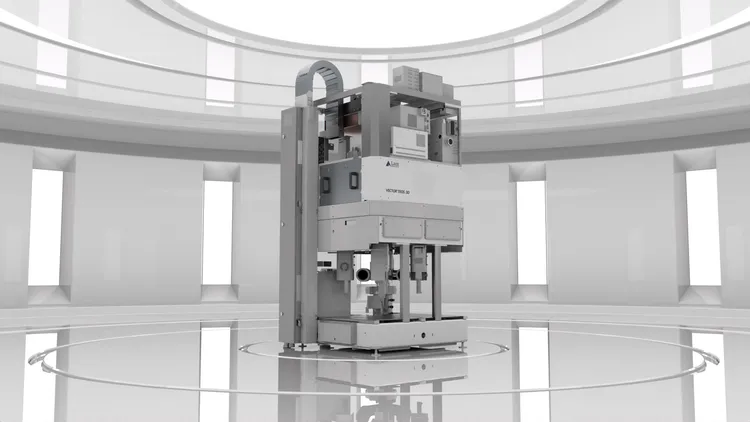

近年 AI 应用的爆炸性成长,带动市场对高效能运算晶片的庞大需求。晶片制造商纷纷导入 3D 先进封装与小晶片(chiplet)架构,将记忆体与处理单元紧密结合,借此缩短电路路径、提升处理速度与效能。然而,随著堆叠高度与复杂度提升,制程挑战同步增加,晶圆应力引发的翘曲、以及薄膜裂缝与空隙都可能降低良率。VECTOR TEOS 3D 正是为此而生,能以奈米级精度沉积厚达 60 微米的介电薄膜,并具备延展至 100 微米以上的能力。这类薄膜不仅支撑结构与热力学需求,还能避免层状剥离等常见封装失效。

在硬体设计上,TEOS 3D 内建 Lam Research 独创的翘曲晶圆载盘技术,并配合最佳化的载盘设计,能于处理厚晶圆时维持稳定性,即便面对极端翘曲状况,依旧可实现均匀沉积效果。这项突破大幅提升先进封装的制程可行性,让高良率量产成为可能。

Lam Research 在先进封装领域已深耕逾 15 年,并在介电薄膜沉积累积数十年的专业经验。VECTOR TEOS 3D 建立于既有的 VECTOR Core 与 TEOS 系列基础上,不仅象征该公司在整合封装材料与制程创新上的持续进展,更进一步强化其在全球半导体供应链的领先地位。官方表示,TEOS 3D 是完整产品组合中的关键拼图,未来将持续推动制程效率、良率与生产力,助力晶片制造商在 AI 与 HPC 的浪潮下抢占市场先机。

點擊閱讀下一則新聞

點擊閱讀下一則新聞